PCB 아트웍으로 EMI/EMC 규제 준수 및 노이즈 감소 방법

PCB 아트웍 설계에서 EMI/EMC 성공은 80%가 결정됩니다. 전자제품의 높은 회로 밀도와 동작 속도에서 노이즈 감소를 위한 설계 전략과 실무 기법을 소개합니다.

도입: 왜 PCB 아트웍이 EMI/EMC 성공의 80%를 좌우하는가

전자제품의 동작 속도가 GHz 영역으로 진입하고 회로 밀도가 높아지면서, EMI(전자기 간섭)와 EMC(전자기 적합성) 문제는 더 이상 회로도 단계에서만 해결할 수 있는 영역이 아닙니다. 실제로 동일한 회로도라도 PCB 아트웍을 누가, 어떻게 그렸느냐에 따라 방사 노이즈 측정값이 10dB 이상 차이 나는 사례가 흔하게 보고됩니다.

EMI 문제는 일반적으로 세 가지 요소의 조합으로 발생합니다.

- 노이즈 소스(Source): 스위칭 IC, 클럭, 고속 디지털 신호 등

- 전파 경로(Coupling Path): 트레이스, 플레인, 케이블, 공기를 통한 결합

- 피해 회로(Victim): 아날로그 회로, RF 수신부, 외부 장비 등

이 중 PCB 설계자가 가장 직접적으로 통제할 수 있는 영역은 전파 경로입니다. 노이즈 소스 자체를 제거하기 어렵고, 피해 회로의 민감도를 바꾸기도 쉽지 않지만, 경로는 레이아웃을 통해 의도적으로 설계할 수 있습니다.

인증 단계에서 EMC 이슈가 발견되면 보드 재설계, 시제품 재제작, 인증 재시험까지 이어지며 일반적으로 수 주에서 수 개월의 출시 지연이 발생합니다. 설계 초기에 EMC를 고려하는 것이 가장 저렴한 대응입니다.

1. EMC 설계의 출발점: 견고한 접지(GND) 플레인 전략

1.1 저임피던스 GND 플레인의 역할

많은 신입 엔지니어들이 GND를 단순한 '0V 기준점'으로 이해하지만, 고속 회로에서 GND 플레인은 두 가지 핵심 역할을 동시에 수행합니다.

- 신호 리턴 경로: 모든 신호 전류는 반드시 소스로 되돌아가야 하며, 고주파 신호는 인덕턴스가 가장 낮은 경로(즉, 신호 트레이스 바로 아래)를 따라 흐릅니다.

- 차폐막(Shield): 연속된 GND 플레인은 EM 파의 방사를 억제하고 외부 노이즈로부터 신호를 보호합니다.

GND 플레인이 슬롯이나 분할로 끊어지면, 리턴 전류는 우회 경로를 찾게 되고 결과적으로 큰 루프 면적을 형성합니다. 루프 면적이 커질수록 방사 노이즈는 비례하여 증가하므로, GND 플레인의 연속성 유지는 EMC 설계의 첫 번째 원칙입니다.

1.2 아날로그/디지털 혼재 보드의 GND 분리 원칙

아날로그와 디지털이 함께 있는 보드에서 "GND를 분리할 것인가, 통합할 것인가"는 오랫동안 논쟁이 되어온 주제입니다. 통상적인 실무 가이드는 다음과 같습니다.

- 대부분의 일반적인 디지털/아날로그 혼재 회로는 통합 GND 플레인이 더 안전한 선택입니다.

- 고분해능 ADC, 정밀 계측, 무선 RF 등 특수한 경우에 한해 분할 GND를 적용하되, 신호 트레이스가 분할선을 가로지르지 않도록 라우팅 영역을 사전에 분리합니다.

- 분할 GND를 사용할 경우 단일 지점 연결(Star Point)은 ADC 칩 바로 아래나 변환기 근처에 두는 것이 일반적입니다.

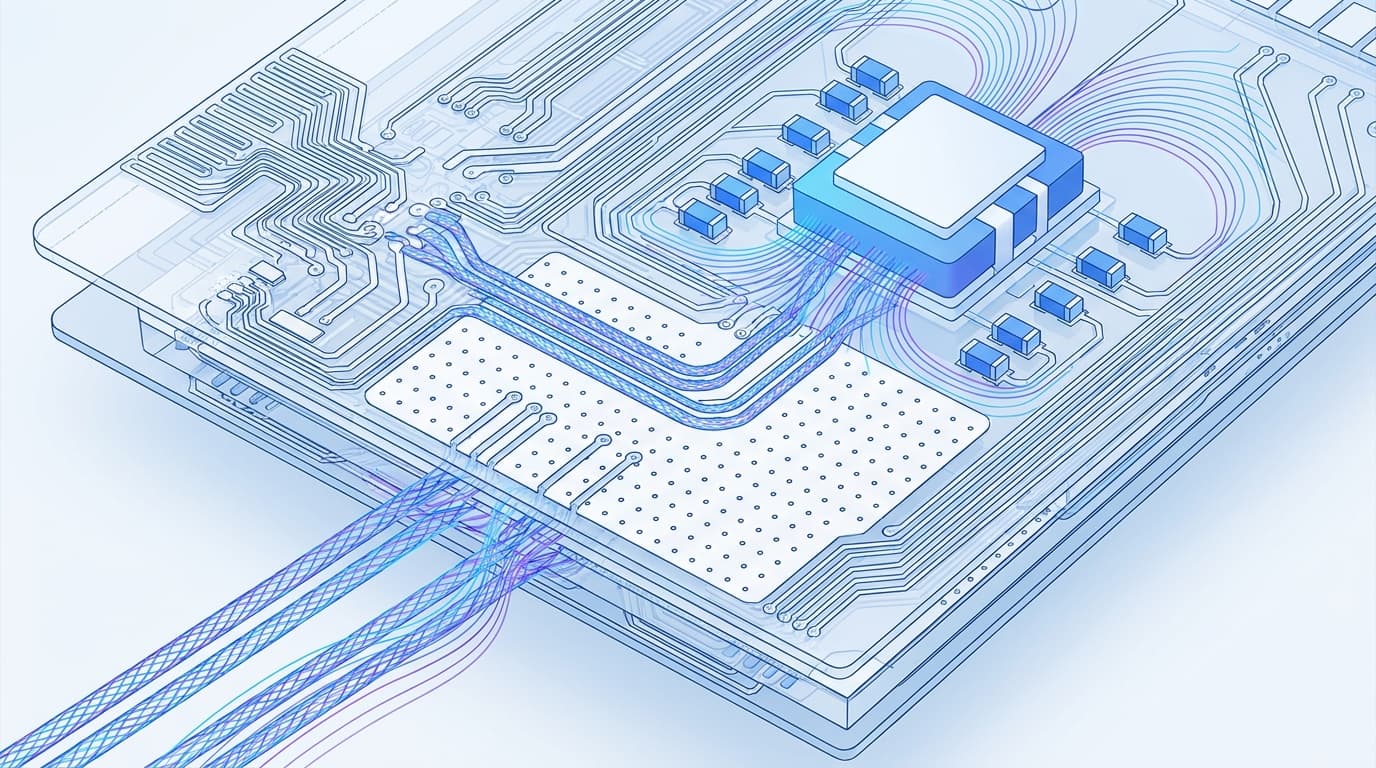

1.3 Via 스티칭과 GND 연속성 확보

다층 보드에서는 GND Via 스티칭(stitching)을 통해 여러 층의 GND 플레인을 전기적으로 단단히 묶어주는 작업이 필요합니다.

- 보드 외곽을 따라 GND Via를 촘촘히 배치하여 가장자리 방사를 억제

- 고속 신호 트레이스 양옆에 가드 Via를 동반 배치

- 일반적으로 권장되는 스티칭 간격은 관심 주파수의

λ/20~λ/10수준

PCB ground plane with via stitching pattern around board edge and high-speed traces

PCB ground plane with via stitching pattern around board edge and high-speed traces

2. 부품 배치(Placement)에서 결정되는 EMI 성능

2.1 기능 블록별 그룹화 원칙

EMI 성능의 절반 이상은 라우팅을 시작하기 전, 부품 배치 단계에서 이미 결정됩니다. 기본 원칙은 "비슷한 것끼리 모으고, 다른 것끼리 멀리 둔다"입니다.

- 고속 디지털(MCU, FPGA, DDR 등)

- 아날로그/센서 회로

- 전원부(SMPS, LDO 등)

- I/O 커넥터 영역

이 네 가지를 물리적으로 구분하여 배치하고, 노이즈가 강한 블록(SMPS, 클럭)과 민감한 블록(ADC, RF) 사이에는 가능한 한 거리를 확보합니다. 보드 면적 제약이 심하더라도 최소한 인접 배치는 피해야 합니다.

2.2 디커플링 커패시터 배치의 황금률

디커플링 커패시터는 IC 전원 핀에 가능한 한 가깝게 배치해야 합니다. 이유는 단순합니다. 커패시터에서 IC까지의 트레이스 인덕턴스가 PDN(전원분배망) 임피던스를 결정하기 때문입니다. 거리가 멀어질수록 고주파에서의 디커플링 효과가 급격히 떨어집니다.

실무에서 일반적으로 사용되는 조합은 다음과 같습니다.

0.01µF ~ 0.1µF: 고주파 노이즈 디커플링용, IC 전원 핀에 가장 가깝게1µF: 중주파 영역 보강10µF이상: 저주파 및 벌크 디커플링용

여러 용량을 병렬로 사용하는 이유는 각 커패시터의 자기공진주파수(SRF)가 다르기 때문이며, 조합을 통해 넓은 주파수 대역에서 낮은 임피던스를 유지할 수 있습니다.

2.3 커넥터와 I/O 영역의 격리

케이블은 보드 외부로 노이즈를 방사하는 가장 효율적인 안테나 역할을 합니다. 따라서 I/O 커넥터 주변에는 다음과 같은 처리가 권장됩니다.

- 커넥터 근처에 Quiet GND 영역을 별도로 두고, 노이즈가 많은 디지털 GND와 비드(Bead) 또는 단일 지점으로 연결

- 커넥터 핀 근처에 ESD/필터 부품(TVS, 커먼모드 초크, π 필터)을 배치

- 고속 디지털 부품을 커넥터 바로 옆에 두지 않기

3. 트레이스 라우팅: 디테일이 결과를 바꾼다

3.1 고속 신호 라우팅의 기본 규칙

고속 신호의 트레이스는 다음 원칙을 따릅니다.

- 최단 경로: 길이가 짧을수록 방사도, 지연도, 손실도 줄어듭니다.

- 45도 또는 곡선 라우팅: 90도 직각 코너는 임피던스 불연속과 미세한 방사를 유발합니다.

- 임피던스 매칭: 일반적으로 단일 종단은

50Ω, 차동 신호는90Ω또는100Ω이 표준이며, 스택업과 트레이스 폭으로 제어합니다. - 차동 페어: 길이 매칭(통상 수 mil 이내), 간격 일정 유지, 동일 레이어 사용

3.2 리턴 경로(Return Path) 의식적 설계

고주파 신호의 리턴 전류는 신호 트레이스 바로 아래의 GND 플레인을 따라 흐릅니다. 이때 신호 트레이스가 GND 플레인의 갭이나 슬롯 위를 지나가면, 리턴 전류는 우회해야 하고 큰 루프 안테나가 형성됩니다.

특히 신호가 레이어를 변경할 때 주의가 필요합니다.

- 가능하면 동일한 GND 플레인을 기준으로 하는 레이어 간 이동

- 레이어 변경 Via 옆에 GND Via를 동반 배치하여 리턴 경로 제공

- 전원 플레인을 가로질러 신호가 이동하는 경우, 스티칭 커패시터로 AC 리턴 경로 확보

3.3 클럭 및 고주파 신호의 특별 관리

클럭은 EMI의 가장 큰 단일 원인입니다. 기본 주파수뿐 아니라 고조파(harmonics)가 GHz 대역까지 확장되기 때문입니다. 일반적인 처리 기법은 다음과 같습니다.

- 클럭 라인은 내부 레이어(GND 플레인 사이)로 라우팅하여 자연스러운 차폐 활용

- 가드 트레이스(GND로 양 끝과 중간을 Via로 묶은 트레이스) 적용

- 다른 신호와의 간격은 트레이스 폭의

3W이상 확보 - 가능한 경우 스프레드 스펙트럼 클럭(SSC) 활용

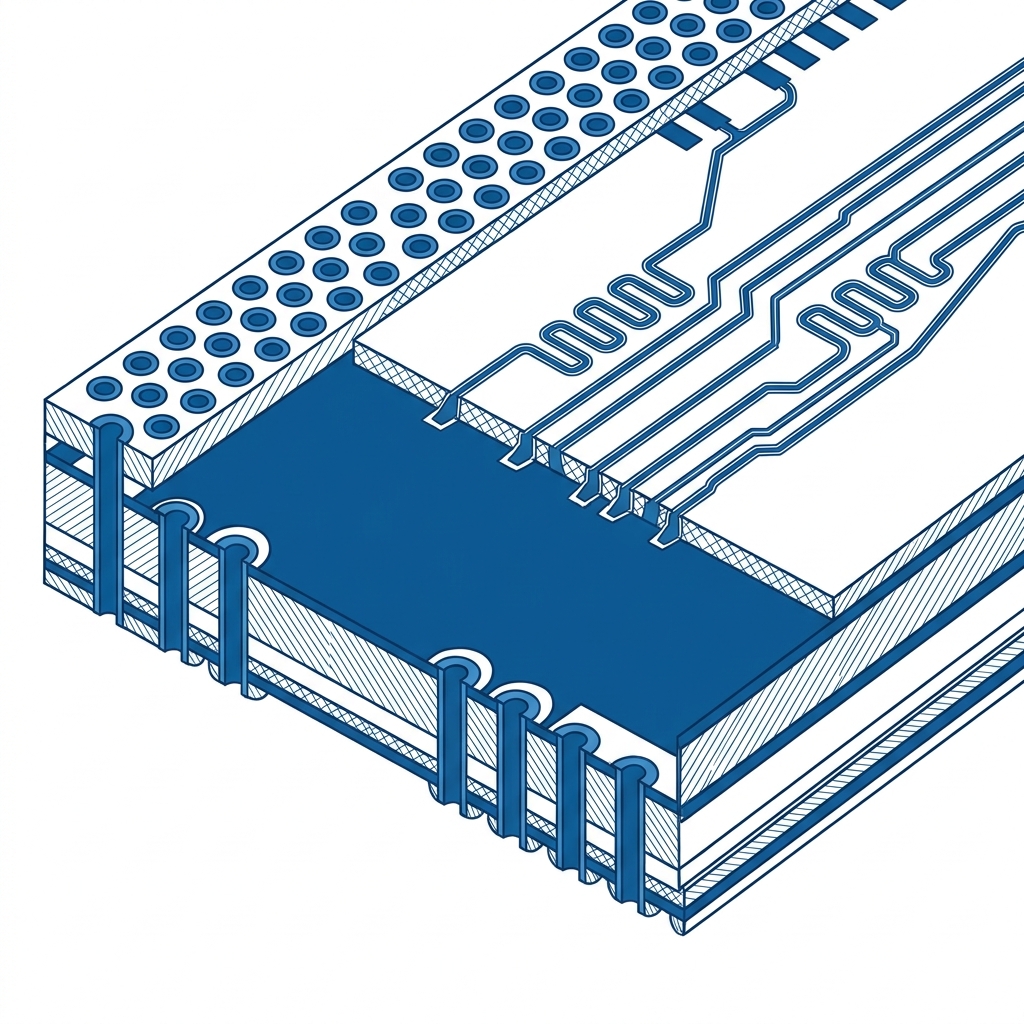

Multilayer PCB stack-up showing signal layers adjacent to ground planes

Multilayer PCB stack-up showing signal layers adjacent to ground planes

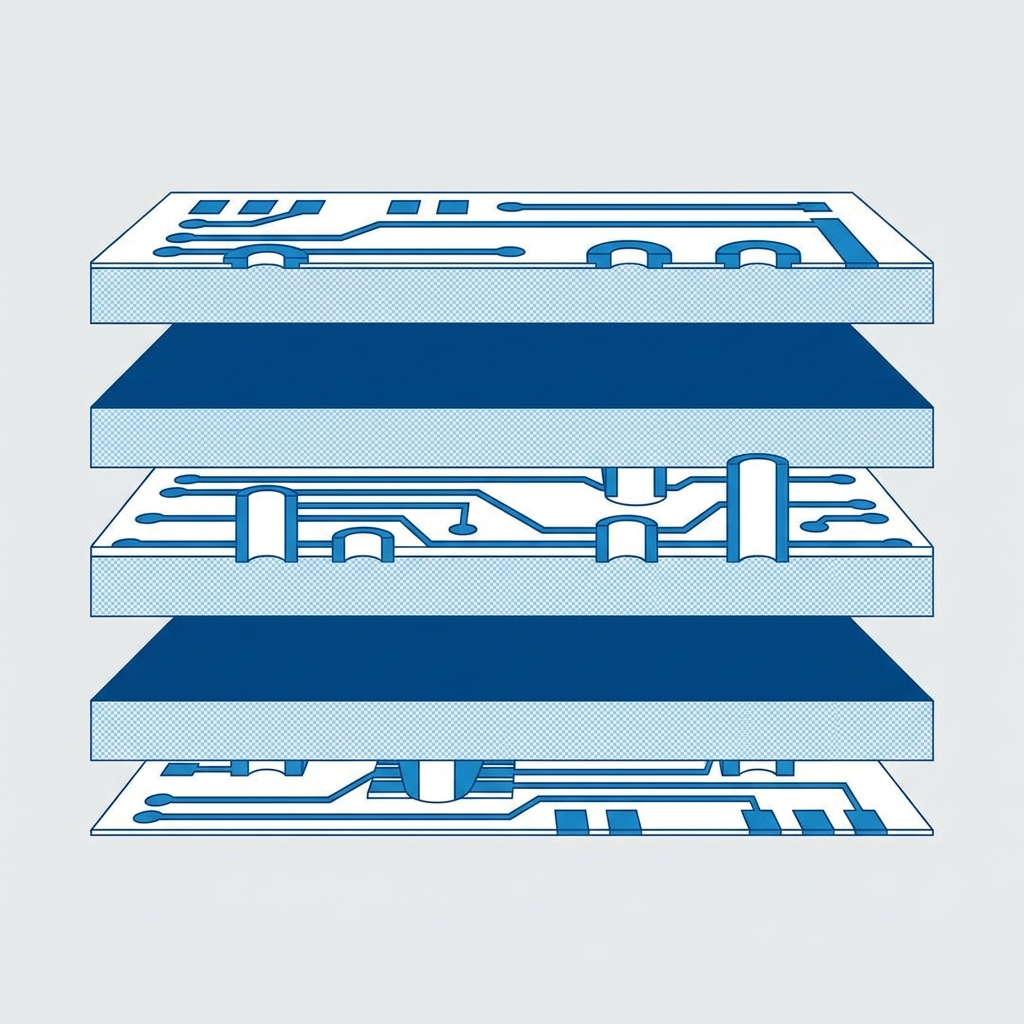

4. 스택업(Stack-up) 설계와 전원 분배망(PDN)

4.1 다층 PCB 스택업 구성 원칙

스택업은 EMC 성능의 기반입니다. 일반적으로 권장되는 구성은 다음과 같습니다.

- 4층 보드: Signal / GND / Power / Signal — 단, 외층 신호의 리턴 경로가 약하므로 고속 신호는 가급적 GND 인접 내부층 활용을 권장하는 의견도 많음

- 6층 보드: Signal / GND / Signal / Power / GND / Signal 또는 Signal / GND / Signal / GND / Power / Signal

- 8층 이상: 모든 신호 레이어가 GND 플레인에 인접하도록 배치하는 것을 일반적인 목표로 함

핵심 원칙은 모든 신호 레이어 바로 옆에 연속된 GND 플레인을 두는 것입니다. 이렇게 하면 리턴 경로가 안정되고, 임피던스 제어가 쉬워지며, 방사 노이즈가 자연스럽게 억제됩니다.

4.2 전원 플레인과 GND 플레인의 커플링

전원 플레인과 GND 플레인을 얇은 유전체(prepreg)로 가깝게 붙이면, 두 플레인 사이에 분포된 평면 캐패시턴스가 형성됩니다. 이 평면 캐패시턴스는 다음과 같은 이점을 제공합니다.

- 고주파 영역에서 디커플링 커패시터의 인덕턴스 한계를 보완

- PDN 임피던스를 광대역에서 낮은 수준으로 유지

- 전원 노이즈 방사 감소

유전체 두께를 통상적으로 3mil 이하로 가깝게 두는 설계가 고성능 보드에서 자주 사용됩니다.

5. Shift-Left: 설계 초기 시뮬레이션과 표준 대응

5.1 SI/PI/EMC 시뮬레이션의 조기 도입

레이아웃을 확정하고 시제품을 만든 후 EMC 챔버에서 문제를 발견하는 것은 가장 비싼 방식입니다. 최근에는 설계 초기 단계에 시뮬레이션을 적극적으로 활용하는 Shift-Left 방식이 일반적입니다.

일반적으로 활용되는 시뮬레이션 항목은 다음과 같습니다.

- 임피던스 제어 검증(스택업 단계)

- 크로스토크 분석(라우팅 단계)

- PDN 임피던스 분석(디커플링 설계 단계)

- Eye diagram 및 타이밍 마진 분석

- 방사 노이즈 사전 추정(전체 보드 단계)

5.2 국제 EMC 표준 개요

제품을 출시하려면 해당 시장과 제품군에 맞는 EMC 표준을 충족해야 합니다. 자주 인용되는 표준은 다음과 같습니다.

- FCC Part 15: 미국 시장의 의도/비의도 방사기 규제

- CISPR 32 / EN 55032: 멀티미디어 장비의 방사·전도 노이즈

- CISPR 35 / EN 55035: 멀티미디어 장비의 내성(Immunity)

- IEC 61000 시리즈: ESD, EFT, Surge 등 내성 시험 전반

- CISPR 25, ISO 11452: 자동차 전장 부품용

제품군에 따라 의료기기(IEC 60601-1-2), 산업용(IEC 61000-6-x), 무선기기(EN 300 시리즈) 등 별도의 표준이 적용되므로 사전 확인이 필요합니다.

5.3 사전 측정(Pre-compliance Test)의 가치

공식 인증 시험은 비용과 시간이 많이 들기 때문에, 자체적으로 사전 측정을 수행하는 것이 일반적입니다.

- 근접장 프로브(Near-field probe): 보드 위 노이즈 핫스팟을 시각적으로 발견

- 스펙트럼 분석기 + LISN: 전도 노이즈 사전 측정

- 간이 안테나 + 챔버: 방사 노이즈의 대략적 경향 파악

이러한 사전 측정으로 발견된 이슈를 빠르게 수정하면, 설계-시제품-검증 루프를 짧게 유지할 수 있어 전체 개발 일정을 안정화할 수 있습니다.

결론: EMC는 사후 대응이 아닌 설계 철학

EMI/EMC 성능은 마지막에 페라이트 비드 하나, 차폐 캔 하나로 해결되는 영역이 아닙니다. 접지 전략, 부품 배치, 트레이스 라우팅, 스택업, 시뮬레이션이라는 다섯 축이 설계 초기부터 일관된 철학으로 적용되어야 비로소 안정적인 결과를 얻을 수 있습니다.

실무에 적용할 수 있는 핵심 체크리스트를 정리하면 다음과 같습니다.

- 모든 신호 레이어가 연속된 GND 플레인에 인접하도록 스택업을 설계한다.

- 기능 블록을 구분하여 배치하고, 노이즈원과 민감 회로를 분리한다.

- 디커플링 커패시터는 IC 전원 핀에 가능한 한 가깝게 배치한다.

- 고속 신호의 리턴 경로를 의식적으로 설계하고, 레이어 변경 시 GND Via를 동반한다.

- I/O 커넥터 영역은 격리하고 필터·보호 부품을 배치한다.

- 설계 초기에 SI/PI 시뮬레이션을 수행하고, 시제품 단계에서 사전 EMC 측정을 거친다.

EMC를 설계 후반의 골칫거리가 아니라 처음부터 함께 가는 동반자로 받아들일 때, 인증은 통과해야 할 장벽이 아닌 자연스러운 결과가 됩니다. 오늘 다룬 원칙들이 다음 프로젝트의 첫 도면에서부터 살아 있는 가이드가 되기를 바랍니다.